Alice&Bob的新方法用1500个物理量子比特实现了100个逻辑量子比特

法国的研究人员此前开发了一种新型量子纠错架构,他们表示利用这种架构可以在2024年底前开发出实用的容错量子计算机。近日,法国量子初创公司Alice&Bob宣布开发出一种更简单的容错并行逻辑门架构,且无需增加量子计算机在硬件设计方面的复杂性。

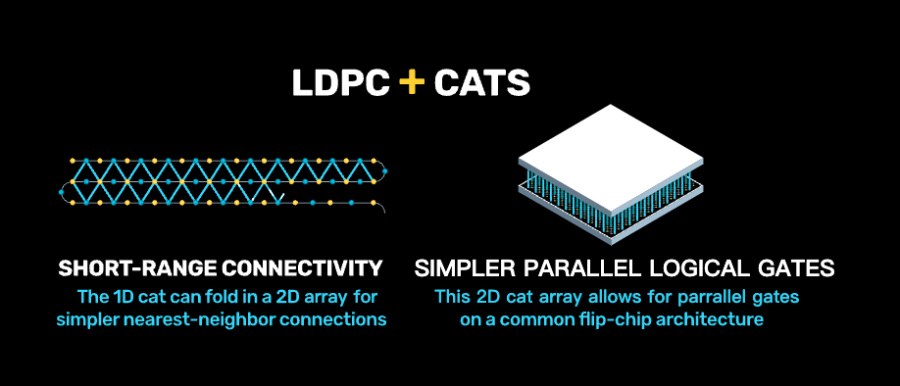

由Alice&Bob公司与法国国家信息与自动化研究所(Inria)共同开展的这项研究,通过在cat(猫)量子比特上使用低密度奇偶校验(LDPC)纠错码的新方法,从而减少了实用量子计算机中所需的量子比特数量。

该方法只需1500个物理量子比特就能编码出100个高度可靠的逻辑量子比特,这为实用的商业应用建立了可行的路径。此外,这项研究使得在量子芯片上实现门以及使用短程连接成为了可能。

量子纠错所需的开销因此而减少,这种方法只需要1500个物理猫态量子比特就能运行100个高保真的逻辑量子比特。Alice&Bob公司目前已经流片了一款芯片,该芯片将对其第一个逻辑量子比特原型“Helium 1”进行编码,以支持未来能够在100个逻辑量子比特和只需1500个物理量子比特的情况下就能运行容错算法。

Alice&Bob公司的首席执行官Théau Peronnin说:“这种使用LDPC码和猫量子比特的新架构可以在不到10万个物理量子比特的情况下运行Shor算法,这比竞争对手需要2000万个量子比特的数量要求降低了200倍。我们的方法使量子计算机在时间、成本和能耗方面更加现实,这表明我们将继续致力于利用纠错逻辑量子比特来推动具有影响力的量子计算之路。”

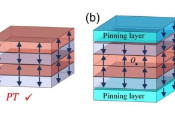

Alice&Bob公司开发的猫量子比特方法已经实现了逻辑量子比特设计,由于猫量子比特具有能避免“比特翻转”错误的固有特性,因此需要的量子比特数量大大减少。在Alice&Bob和CEA之前合作发表的一篇论文中,他们展示了如何用35万个猫量子比特来运行肖尔算法,这比现有技术提高了60倍。

LDPC码是一类高效的纠错码,它可以减少量子计算机纠错时所需的硬件需求。在猫量子比特架构上使用LDPC码的这项最新研究不仅展示了如何进一步减小容错量子计算机所需的量子比特资源,还成功克服了在实施量子LDPC码(qLDPC)过程中的两个关键挑战。(编译:Tmac)