新研究证明为量子计算机添加存储单元可显着减少量子位开销

量子计算系统是基于量子理论关键原理而开发的计算机系统,它在速度和性能方面都可以显着优于传统计算系统。因此,在过去十年左右的时间里,世界各地许多物理学家一直在努力开发这些系统并评估它们的潜力。

比特编码的信息以二进制值(即1或0)表示,量子计算机使用的信息单元是量子比特。量子比特是经典比特的量子力学模拟,它可以是1或0,也可以两者同时存在。

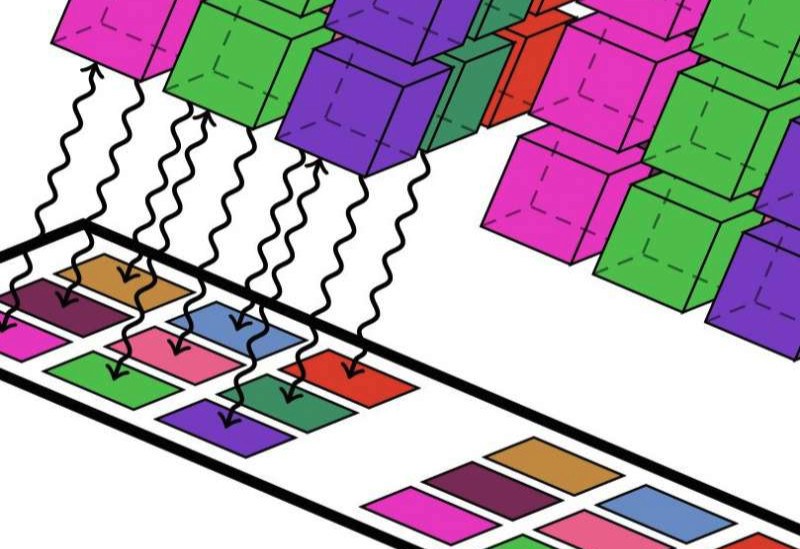

迄今为止开发的大多数量子计算系统都包含一系列放置在2D芯片上的量子比特,它们直接计算信息。而另一方面,经典计算机由处理信息的处理器和存储信息的存储器组成。

来自法国巴黎萨克雷大学、CNRS、CEA的研究人员最近开展了一项研究,他们评估了具有类似于传统计算机结构的量子计算机的性能。其研究结果发表在《物理评论快报》上,研究表明将量子信息存储单元纳入量子计算系统可以创建能显着减少量子比特数量的处理器设备。

进行这项研究的研究人员之一Élie Gouzien说:“通常的量子计算机架构包括将所有量子比特放置在2D芯片上,并直接在这些量子比特上运行计算。在我们的工作中,我们想挑战在单个处理器上拥有所有量子比特的想法,并研究了另一种架构,它更接近经典计算机架构,其中的小型处理器与内存相结合。”

为了有效地将他们的架构与现有的量子计算系统进行比较,Gouzien和他的同事决定评估他们运行给定算法的能力。更具体地说,他们评估了他们的架构运行该算法所需的资源,包括纠错开销。

Gouzien说:“我们详细地将算法分解为基本门,使其适应正在研究的架构,我们还考虑了纠错的开销。然后将这两部分放在一起来评估运行分解算法所需的物理资源。”

研究人员表明,使用由13,436个物理量子比特组成的处理器和可存储2800万个空间模式和45个时间模式的内存,2048 位RSA整数能在177天内用3D仪表色码进行分解。他们还建议每秒插入存储量子比特的额外纠错步骤,这只会将运行时间增加约23%。该团队发现,他们还可以通过增加处理单元中的量子比特数量来缩短运行时间和存储时间。

总体而言,Gouzien和他的同事发现,添加内存组件可以显着减少量子计算系统处理器内的量子比特数量。在他们的论文中,该团队称他们的架构可以通过在由超导量子比特组成的处理器和多路复用存储器之间放置一个微波接口来实现。

Gouzien说:“当然,设计高效的量子存储器并非易事,但它已经是一个研究领域,而且比将数百万个量子比特装入低温恒温器更具挑战性,我们希望我们的文章能够激发对量子存储器的研究,并将其导向计算的用途。”(编译:Qtech)